### Augmenting a Microprocessor with Reconfigurable Hardware

by

John Reid Hauser

B.S. (North Carolina State University) 1987B.S. (North Carolina State University) 1987M.S. (University of California, Berkeley) 1994

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Computer Science

in the

# GRADUATE DIVISION of the UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor John Wawrzynek, Chair Professor Randy H. Katz Professor John Strain

Fall 2000

The dissertation of John Reid Hauser is approved:

Chair

Date

Date

Date

University of California, Berkeley

Fall 2000

## Augmenting a Microprocessor with Reconfigurable Hardware

Copyright 2000 by John Reid Hauser

#### Abstract

Augmenting a Microprocessor with Reconfigurable Hardware

by

John Reid Hauser

Doctor of Philosophy in Computer Science University of California, Berkeley

Professor John Wawrzynek, Chair

As VLSI technology continues to improve, configurable hardware devices such as PLDs are progressively replacing many specialized digital integrated circuits. Fieldprogrammable gate arrays (FPGAs) are one class of such devices, characterized by their ability to be reconfigured as often as desired. Lately, FPGAs have advanced to the stage where they can host large computational circuits, giving rise to the study of *reconfigurable computing* as a potential alternative to traditional microprocessors. Most previous reconfigurable computers, however, have been ad hoc designs that are not fully compatible with existing general-purpose computing paradigms.

This thesis examines the problem of combining reconfigurable hardware with a conventional processor into a single-chip device that can serve as the core of a general-purpose computer. The impact of memory cache stalls, of multitasking context switches, and of virtual memory page faults on the design of the reconfigurable hardware is considered. A possible architecture for the device is defined in detail and its implementation in VLSI studied. With basic development tools and a full-fledged simulator, several benchmarks are tested on the proposed architecture and their performance compared favorably against an existing Sun UltraSPARC. Some additional experiences with the architecture are also related, followed by suggestions for future research. To my recently departed mother, who very much wanted to see me get my degree.

# Contents

| Li       | st of | Figur        | es                                             | v         |

|----------|-------|--------------|------------------------------------------------|-----------|

| Li       | st of | <b>Table</b> | s                                              | ix        |

| 1        | Inti  | oducti       | ion                                            | 1         |

| <b>2</b> | Bac   | kgrou        | nd and Motivation                              | 4         |

|          | 2.1   | The p        | otential for reconfigurable computing          | 4         |

|          |       | 2.1.1        | Computing devices                              | 4         |

|          |       | 2.1.2        | Utilizing growing hardware resources           | 7         |

|          |       | 2.1.3        | Limitations of superscalar and VLIW processors | 9         |

|          |       | 2.1.4        | Reconfigurable computing as a new model        | 10        |

|          |       | 2.1.5        | The hybrid machine                             | 11        |

|          | 2.2   | FPGA         | As                                             | 12        |

|          | 2.3   | Previo       | bus FPGA-based systems and their applications  | 14        |

|          | 2.4   | Focus        | of the research                                | 17        |

|          | 2.5   | Relate       | ed work                                        | 20        |

|          |       | 2.5.1        | Concept prototypes                             | 20        |

|          |       | 2.5.2        | Reconfigurable functional units in a processor | 21        |

|          |       | 2.5.3        | Streaming reconfigurable hardware              | 21        |

|          |       | 2.5.4        | Novel reconfigurable hardware for computation  | 23        |

| 3        | Des   | ign Iss      | Sues                                           | <b>24</b> |

|          | 3.1   | Integra      | ating reconfigurable hardware into a computer  | 24        |

|          |       | 3.1.1        | Level of integration                           | 25        |

|          |       | 3.1.2        | Programming paradigm                           | 28        |

|          |       | 3.1.3        | Configuration encoding and loading             | 29        |

|          |       | 3.1.4        | Caching of configurations                      | 32        |

|          |       | 3.1.5        | Array clocking                                 | 34        |

|          |       | 3.1.6        | External interface and access to memory        | 36        |

|          |       | 3.1.7        | Multitasking                                   | 38        |

|          |       | 3.1.8        | Servicing page misses                          | 40        |

|          | 3.2   | Design       | ning reconfigurable hardware for computation   | 41        |

|          |       | 3.2.1        | Dominance of wires                             | 42        |

|          |     | 3.2.2  | Bit-serial, bit-parallel, and bit-pipelined arithmetic                                                                        |

|----------|-----|--------|-------------------------------------------------------------------------------------------------------------------------------|

|          |     | 3.2.3  | Array granularity                                                                                                             |

|          |     | 3.2.4  | Multiplication elements                                                                                                       |

|          | 3.3 | Review | w                                                                                                                             |

|          |     |        |                                                                                                                               |

| 4        |     | -      | Garp Design 60                                                                                                                |

|          | 4.1 | _      | Architecture                                                                                                                  |

|          |     | 4.1.1  | Array organization                                                                                                            |

|          |     | 4.1.2  | Array logic blocks                                                                                                            |

|          |     | 4.1.3  | Array wires                                                                                                                   |

|          |     | 4.1.4  | Array timing                                                                                                                  |

|          |     | 4.1.5  | Support for computational primitives                                                                                          |

|          |     | 4.1.6  | Processor control of array execution                                                                                          |

|          |     | 4.1.7  | Configurations                                                                                                                |

|          |     | 4.1.8  | Array access to memory                                                                                                        |

|          |     | 4.1.9  | Memory queues                                                                                                                 |

|          | 4.2 | Contra | ast with other designs                                                                                                        |

|          | 4.3 | Imple  | mentation study $\ldots \ldots 79$ |

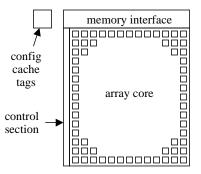

|          |     | 4.3.1  | Overall functional organization                                                                                               |

|          |     | 4.3.2  | Using pass transistors for switching                                                                                          |

|          |     | 4.3.3  | Array wires                                                                                                                   |

|          |     | 4.3.4  | Configuration cache management                                                                                                |

|          |     | 4.3.5  | Logic block layout                                                                                                            |

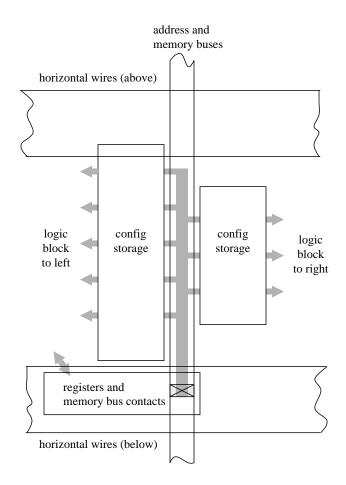

|          |     | 4.3.6  | Configuration storage and distribution                                                                                        |

|          |     | 4.3.7  | Logic block functions                                                                                                         |

|          |     | 4.3.8  | Speed, power, and area 104                                                                                                    |

| <b>5</b> | Ben | chmar  | rks and Statistics 106                                                                                                        |

|          | 5.1 | Hypot  | hetical Garp                                                                                                                  |

|          | 5.2 | • •    | are tools $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $108$                                                |

|          |     | 5.2.1  | The configurator                                                                                                              |

|          |     | 5.2.2  | Linking a configuration into a C program                                                                                      |

|          |     | 5.2.3  | The simulator $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $111$                          |

|          | 5.3 | Hand-  | coded benchmarks                                                                                                              |

|          |     | 5.3.1  | Data Encryption Standard (DES) 114                                                                                            |

|          |     | 5.3.2  | MD5 and SHA hashes                                                                                                            |

|          |     | 5.3.3  | Image dithering                                                                                                               |

|          |     | 5.3.4  | Image median filter                                                                                                           |

|          |     | 5.3.5  | Sorting                                                                                                                       |

|          |     | 5.3.6  | Library functions strlen and strcpy 124                                                                                       |

|          |     | 5.3.7  | Benchmark review                                                                                                              |

|          | 5.4 |        | guration statistics                                                                                                           |

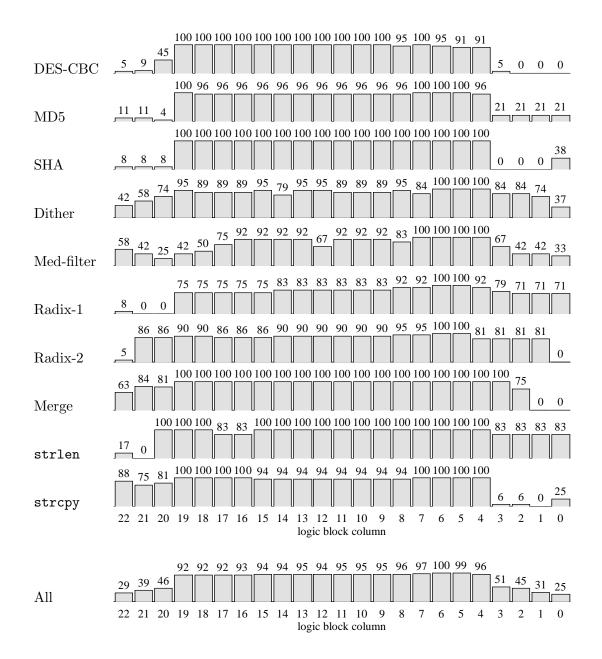

|          | 0.1 | 5.4.1  | Functional density   129                                                                                                      |

|          |     | 5.4.2  | Logic block inputs                                                                                                            |

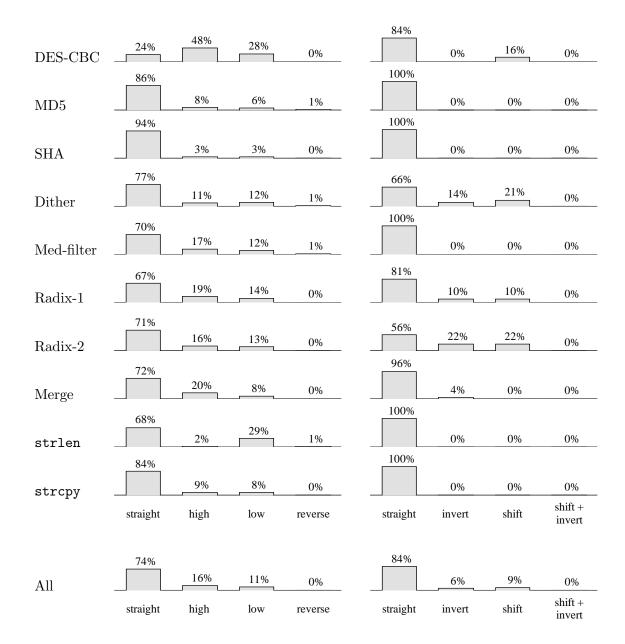

|          |     | 5.4.3  | Logic block functions                                                                                                         |

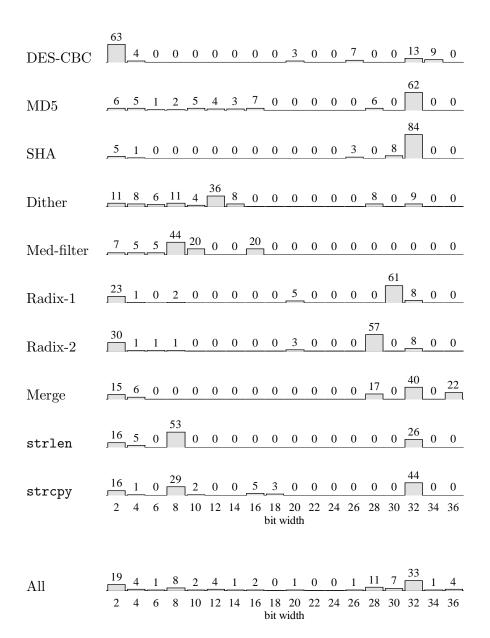

|    |       | 5.4.4 Granularity                                                      | 136       |

|----|-------|------------------------------------------------------------------------|-----------|

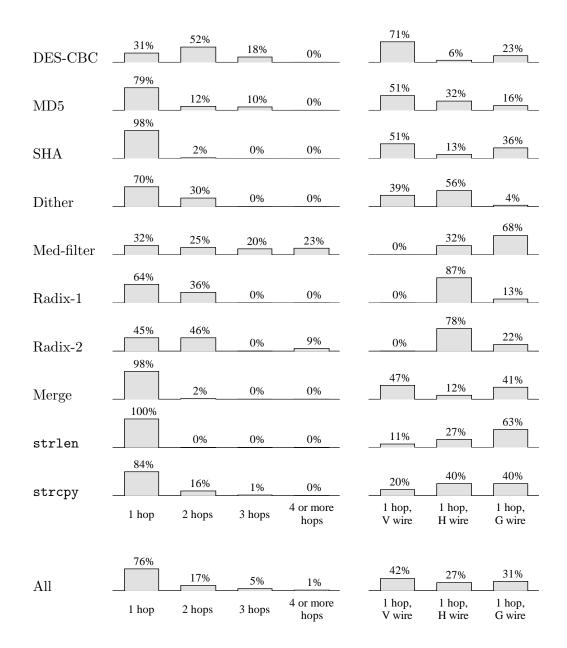

|    |       | 5.4.5 Wire connections                                                 | 140       |

|    |       | 5.4.6 Memory accesses                                                  | 146       |

| 6  | Gar   | o Retrospective                                                        | 149       |

|    | 6.1   | Noteworthy features                                                    | 149       |

|    |       | 6.1.1 Processor handling of start-up, shut-down, and other particulars | 149       |

|    |       | 6.1.2 Support for extended functions in logic blocks                   | 151       |

|    |       | 6.1.3 Limited configuration turnaround                                 | 151       |

|    |       | 6.1.4 Array access to memory                                           | 152       |

|    |       | 6.1.5 Array clocking and context switches                              | 152       |

|    | 6.2   | Corrected mistakes                                                     | 153       |

|    | 6.3   | Weaknesses                                                             | 155       |

|    |       | 6.3.1 Wire network                                                     | 155       |

|    |       | 6.3.2 Memory bottleneck                                                | 156       |

|    |       | 6.3.3 Programming experience                                           | 156       |

| 7  | Con   | clusions                                                               | 159       |

|    | 7.1   | Summary of contributions                                               | 159       |

|    | 7.2   | Application niche                                                      | 160       |

|    | 7.3   | Architectural alternatives                                             | 162       |

|    | 7.4   | Programming challenge                                                  | 163       |

|    | 7.5   | Outlook                                                                | 164       |

| Bi | bliog | raphy                                                                  | 166       |

| Δ  | The   | Garp Architecture                                                      | 177       |

| 11 |       | Introduction                                                           | 177       |

|    |       | Reconfigurable array                                                   | 178       |

|    | 11.2  | A.2.1 Internal wire network                                            | 182       |

|    |       | A.2.2 Logic block configurations                                       | 187       |

|    |       | A.2.3 Logic block functions                                            | 194       |

|    |       | A.2.4 Internal timing                                                  | 203       |

|    | A.3   | Integration of array with main processor                               | 204       |

|    | п.0   | A.3.1 Processor control of array                                       | $20^{-2}$ |

|    |       | A.3.2 Array control blocks                                             | 204       |

|    |       | A.3.3 Array memory queues                                              | 230       |

| Б  | C     |                                                                        | 0.0       |

| в  |       | 11                                                                     | 234       |

|    | B.1   | Single-bit operations                                                  | 234       |

|    | B.2   | Shifts                                                                 | 234       |

|    | B.3   | Using the carry chain                                                  | 235       |

|    | B.4   | Adding or subtracting three terms                                      | 237       |

|    | B.5   | Multiplication                                                         | 238       |

# List of Figures

| 2.1        | A data-flow graph for a simple expression.                                    | 5                                       |

|------------|-------------------------------------------------------------------------------|-----------------------------------------|

| 2.2        | A simplified diagram of an aggressive superscalar or VLIW processor           | 6                                       |

| 2.3        | An application-specific pipeline for computing the graph in Figure 2.1.       | 6                                       |

| 2.4        | A model of a reconfigurable device analogous to Figure 2.2 for a traditional  |                                         |

|            | processor.                                                                    | 10                                      |

| 2.5        | A more practical hybrid machine, combining a traditional processor with a     |                                         |

|            | reconfigurable device.                                                        | 11                                      |

| 2.6        | The reconfigurable structure from Figure 2.4 as it appears in a commercial    |                                         |

|            | FPGA                                                                          | 12                                      |

| 2.7        | A canonical logic block function.                                             | 12                                      |

| 2.8        | Simplified view of a Xilinx 4000-series logic block.                          | 13                                      |

|            |                                                                               |                                         |

| 3.1        | Reconfigurable array attached as a functional unit or via a coprocessor-style | ~ <b>~</b>                              |

|            | register-transfer interface.                                                  | 25                                      |

| 3.2        | A configuration cache with multiple cache planes.                             | 33                                      |

| 3.3        | Bus through the array for loading configurations and for moving data to and   | 07                                      |

| 0.4        | from memory and the main processor register file.                             | 37                                      |

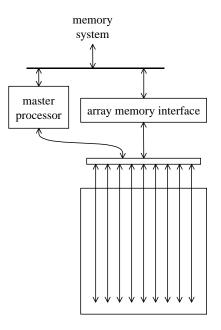

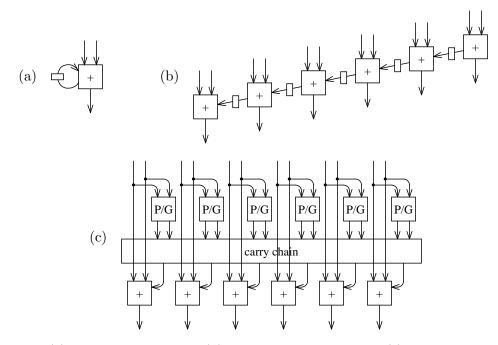

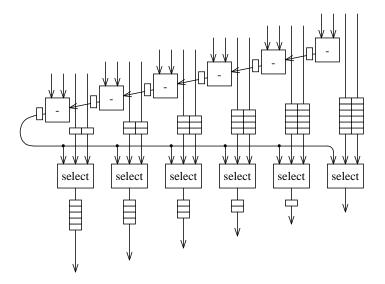

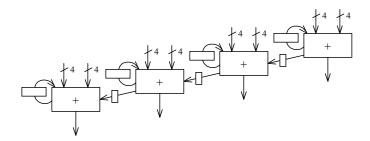

| 3.4        | Bit-serial, bit-pipelined, and bit-parallel addition.                         | 44                                      |

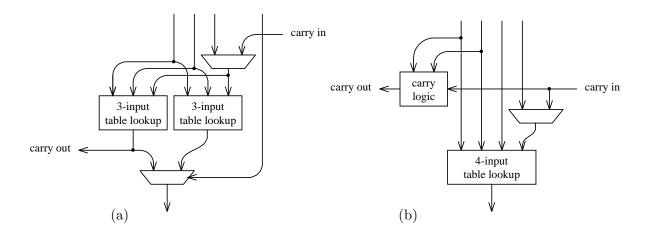

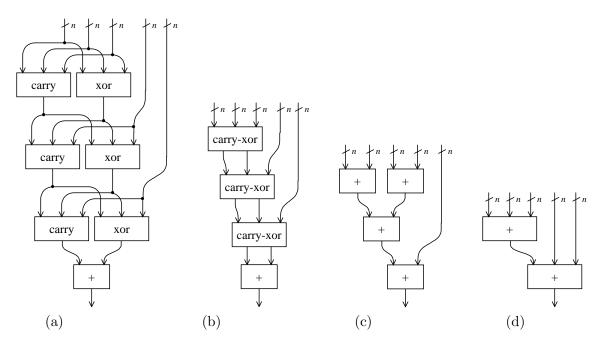

| 3.5        | Possible schemes for inserting a dedicated carry chain into a logic block.    | 46                                      |

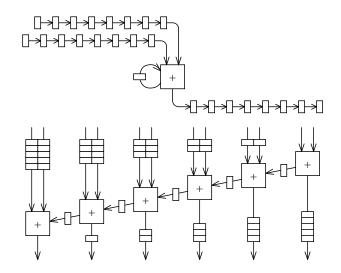

| 3.6        | Skew conversion from bit-parallel to serial or pipelined form and back again. | 46                                      |

| 3.7        | A comparison followed by a multiplexor, implementing the C expression ( $a$   | 477                                     |

| <b>n</b> 0 | < b )? $c$ : $d$                                                              | $\begin{array}{c} 47 \\ 52 \end{array}$ |

| 3.8<br>3.9 | A mixture of parallel, pipelined, and serial techniques.                      | $\frac{52}{56}$                         |

| 5.9        |                                                                               | 50                                      |

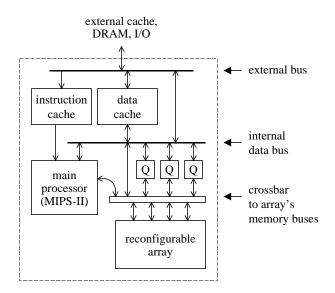

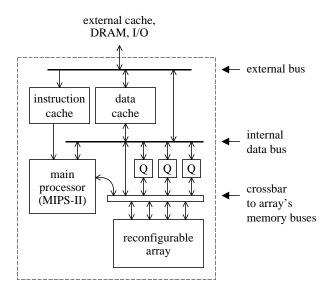

| 4.1        | Overall organization of Garp.                                                 | 61                                      |

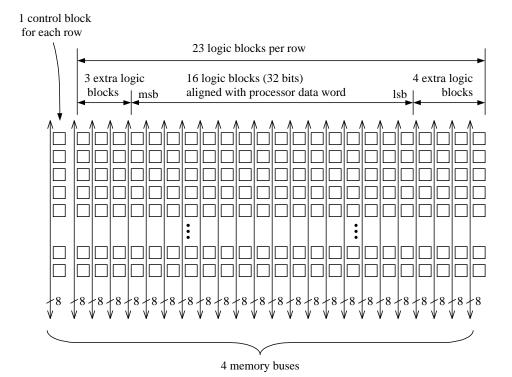

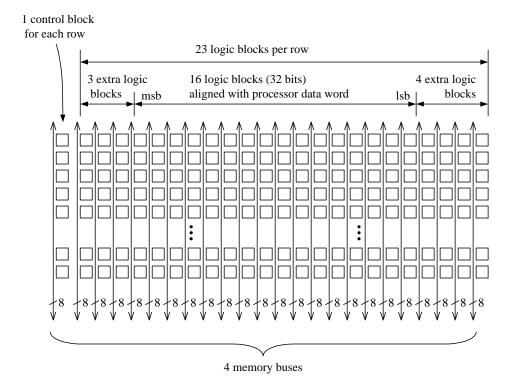

| 4.2        | Garp array organization.                                                      | 62                                      |

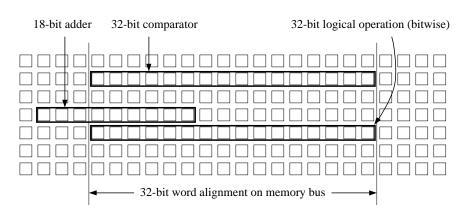

| 4.3        | Typical natural layouts of multi-bit functions.                               | 62                                      |

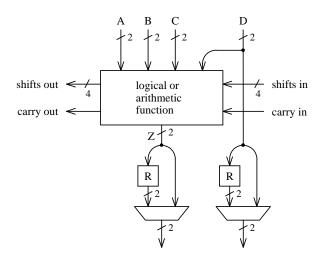

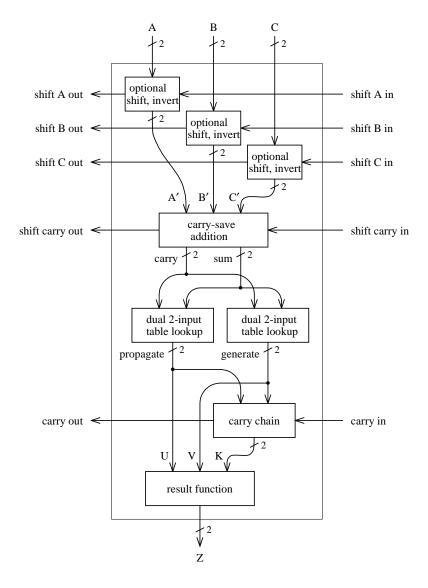

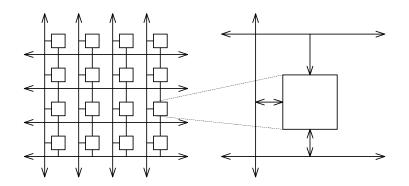

| 4.4        | Simplified logic block schematic.                                             | 64                                      |

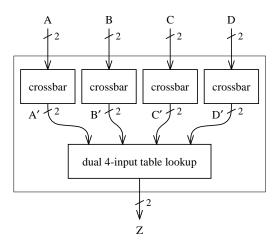

| 4.5        | Simple table-lookup function for a logic block.                               | 65                                      |

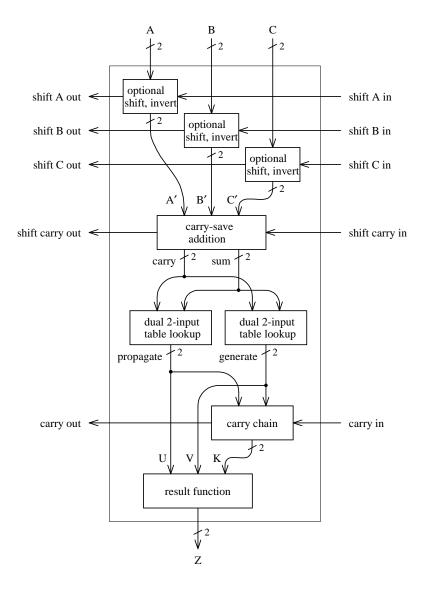

| 4.6        | Logic block triple-add function.                                              | 66                                      |

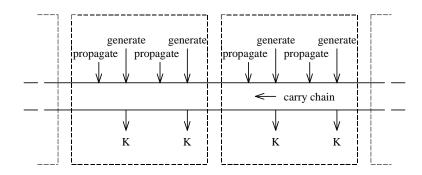

| 4.7        | The carry chain across a row.                                                 | 66                                      |

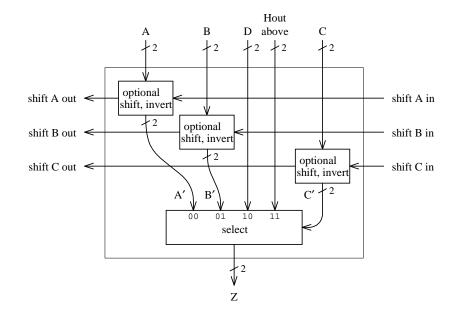

| 4.8        | Logic block select function.                                                  | 67                                      |

|            |                                                                               |                                         |

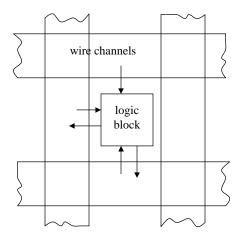

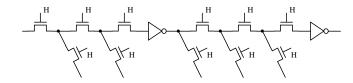

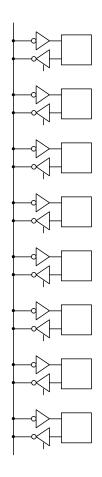

| 4.9                                                                             | The wire channels that can be input and output by a logic block.                          | 68           |  |  |  |  |

|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------|--|--|--|--|

| 4.10                                                                            | ) The pattern of vertical wires (V wires) in a single column of 32 rows.                  |              |  |  |  |  |

|                                                                                 | The horizontal wires (H wires and G wires) between two rows                               |              |  |  |  |  |

|                                                                                 | The four main parts needed to implement the complete Garp array 8                         |              |  |  |  |  |

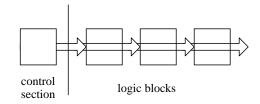

|                                                                                 | Broadcasting control signals across a row from the control block at the end. 83           |              |  |  |  |  |

|                                                                                 | Routing a signal with pass transistors                                                    |              |  |  |  |  |

|                                                                                 | Physical implementation of a wire matching the Garp architecture's logical                |              |  |  |  |  |

|                                                                                 | definition.                                                                               | 85           |  |  |  |  |

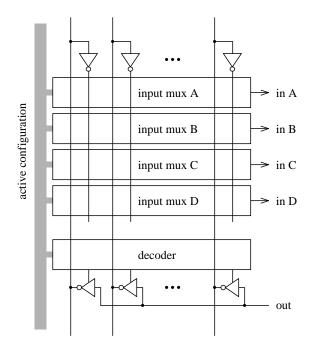

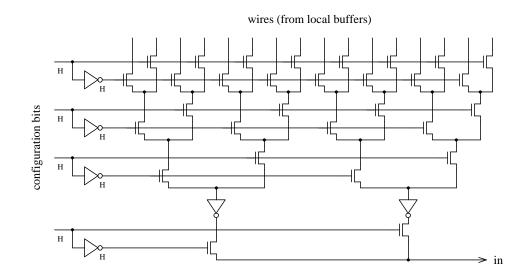

| 4.16                                                                            | The input multiplexors and output drivers underneath the vertical wire chan-              |              |  |  |  |  |

|                                                                                 | nel at a logic block.                                                                     | 86           |  |  |  |  |

| 4.17                                                                            | A single input multiplexor implemented as a binary tree of pass transistors.              | 86           |  |  |  |  |

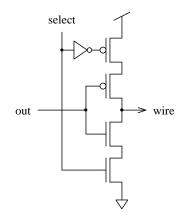

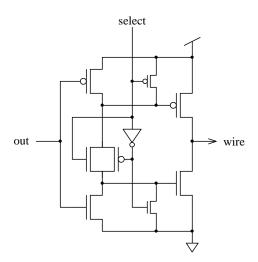

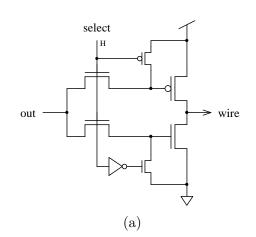

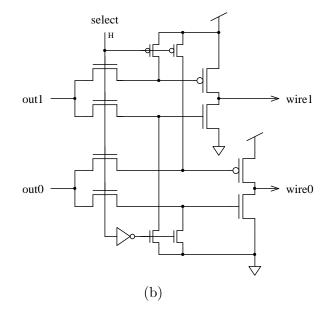

|                                                                                 | A common style of tri-state driver with four transistors in series                        | 88           |  |  |  |  |

| 4.19                                                                            | Another common tri-state driver circuit with only two final transistors in                |              |  |  |  |  |

|                                                                                 | series.                                                                                   | 88           |  |  |  |  |

| 4.20                                                                            | A tri-state driver circuit with only four non-minimal transistors and only two            |              |  |  |  |  |

|                                                                                 | final transistors in series, making use of a higher control voltage for the <i>select</i> |              |  |  |  |  |

|                                                                                 | line                                                                                      | 89           |  |  |  |  |

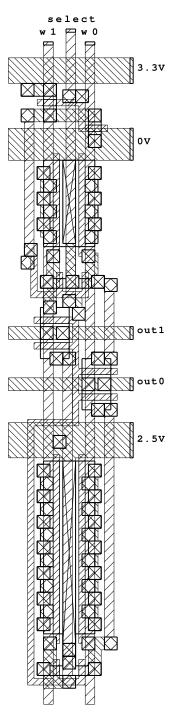

| 4.21                                                                            | Layout underneath the vertical wires for driver circuit in Figure 4.20                    | 89           |  |  |  |  |

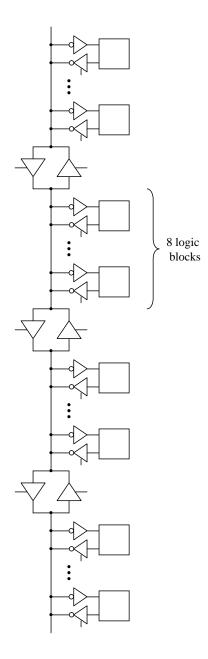

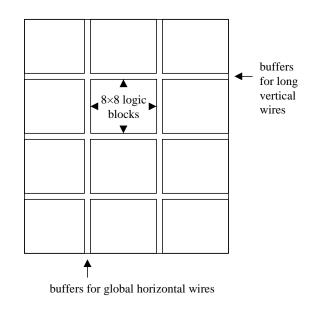

| 4.22                                                                            | Breaking the longer wires into pieces eight logic blocks long joined by con-              |              |  |  |  |  |

|                                                                                 | figurable buffers.                                                                        | 90           |  |  |  |  |

| 4.23                                                                            | The array core as a $4 \times 3$ quilt of patches $8 \times 8$ logic blocks each          | 90           |  |  |  |  |

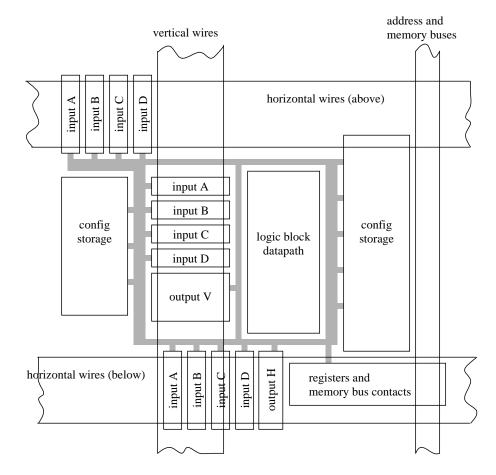

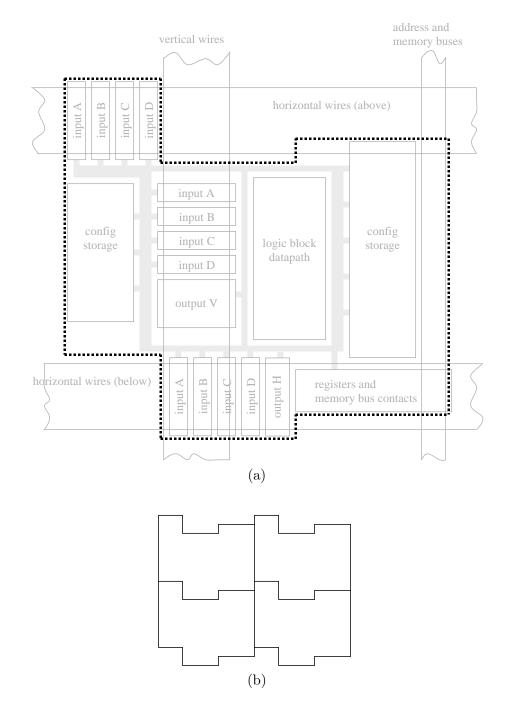

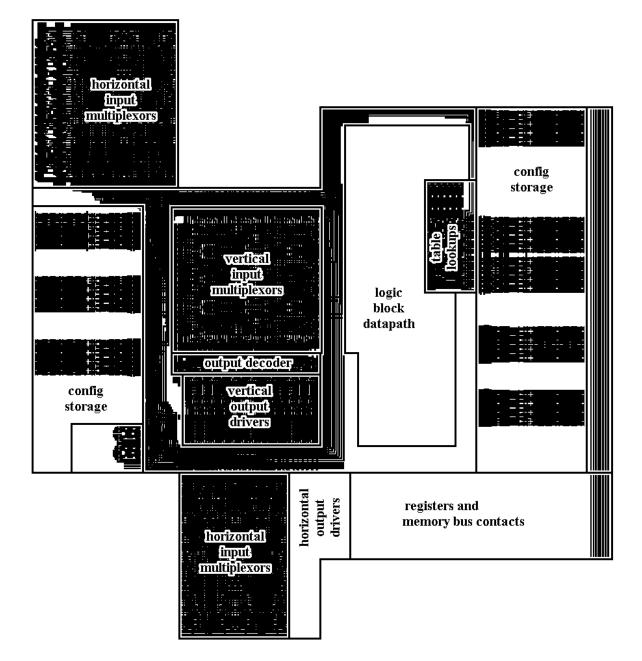

| 4.24                                                                            | Proposed layout organization for a logic block                                            |              |  |  |  |  |

|                                                                                 | Outline of a single logic block tile                                                      |              |  |  |  |  |

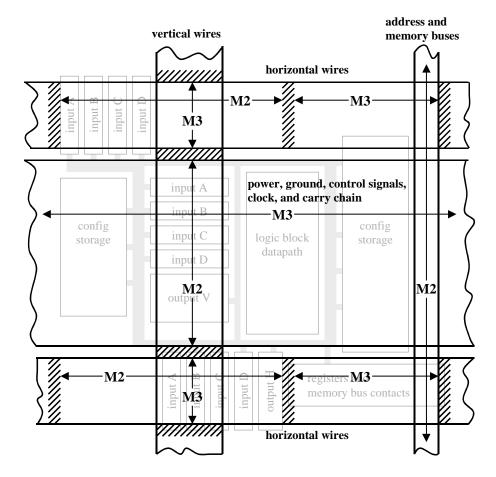

| 4.26                                                                            | Allocation of metal layers 2 and 3 over an individual logic block.                        |              |  |  |  |  |

| 4.27 The relative space assumed for various logic block parts, based on detaile |                                                                                           |              |  |  |  |  |

|                                                                                 | layout for the main density-sensitive components.                                         | 97           |  |  |  |  |

| 4.28                                                                            | Contacts to memory buses, at the boundary between adjacent logic block                    |              |  |  |  |  |

|                                                                                 | tiles                                                                                     | 99           |  |  |  |  |

|                                                                                 | One bit-line in the configuration storage.                                                | 99           |  |  |  |  |

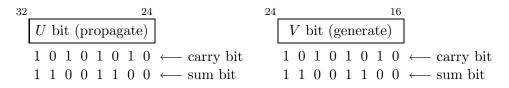

|                                                                                 | 8                                                                                         | 102          |  |  |  |  |

| 4.31                                                                            | Complete contents of the logic block datapath.                                            | 103          |  |  |  |  |

| 5.1                                                                             | Floorplan of the UltraSPARC die, and that of a hypothetical Garp die con-                 |              |  |  |  |  |

| 0.1                                                                             |                                                                                           | 107          |  |  |  |  |

| 5.2                                                                             |                                                                                           | 108          |  |  |  |  |

| 5.2                                                                             |                                                                                           | 115          |  |  |  |  |

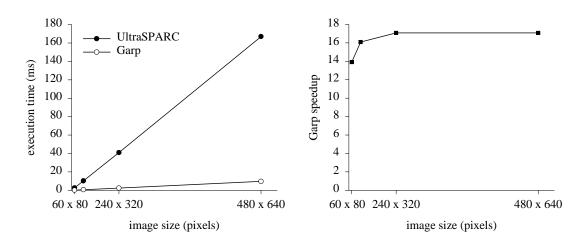

| 5.4                                                                             | -                                                                                         | $117 \\ 117$ |  |  |  |  |

| 5.5                                                                             | -                                                                                         | 119          |  |  |  |  |

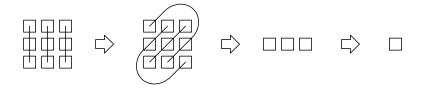

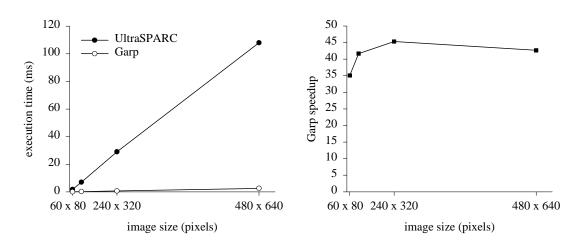

| 5.6                                                                             |                                                                                           | 119          |  |  |  |  |

| 5.7                                                                             |                                                                                           | 121          |  |  |  |  |

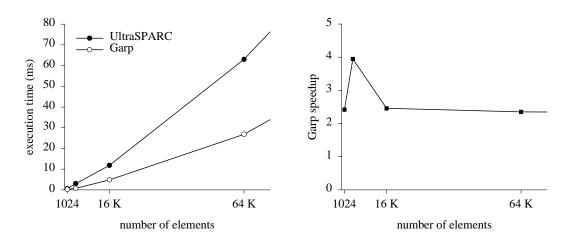

| 5.8                                                                             |                                                                                           | 122          |  |  |  |  |

| 5.9                                                                             |                                                                                           | 123          |  |  |  |  |

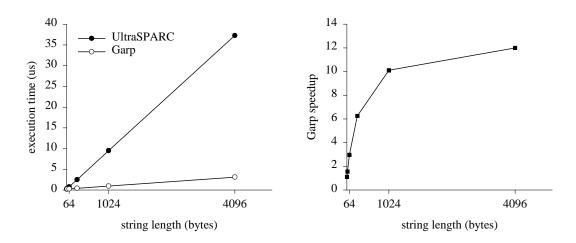

| 5.10                                                                            |                                                                                           | 125          |  |  |  |  |

| 5.11                                                                            |                                                                                           | 125          |  |  |  |  |

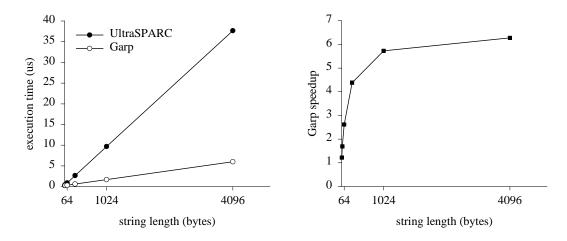

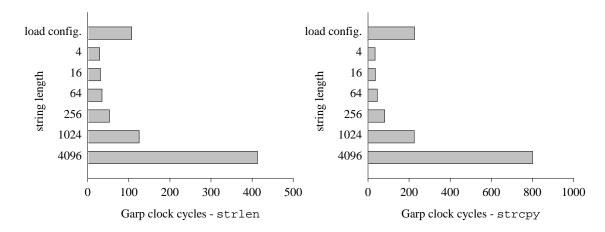

| 5.12  | The time to bring the <b>strlen</b> or <b>strcpy</b> configuration in from DRAM com-<br>pared to the time to execute the function on strings of various lengths                                | 126        |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

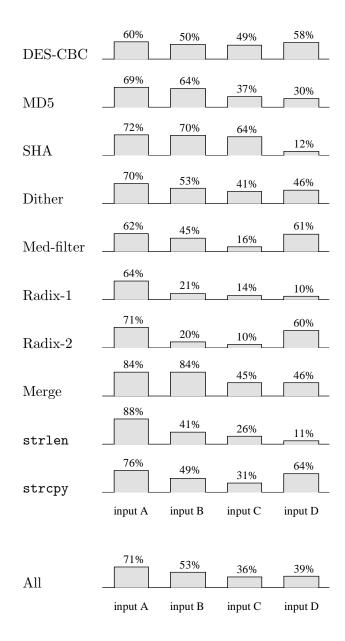

| 5.13  | Connection vector plots for each of the benchmark configurations                                                                                                                               | 142        |

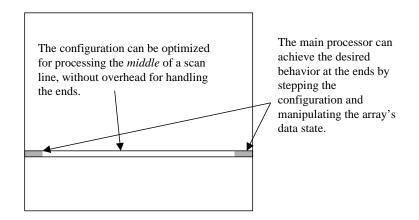

| 6.1   | Typical processing of an image, with a configuration of the reconfigurable hardware capable of handling only the middle of each scan line and the edges being corrected by the main processor. | 150        |

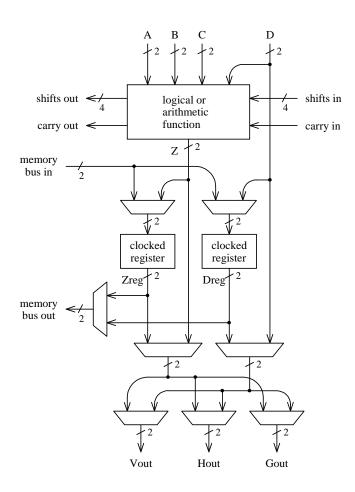

| A.1   | Basic organization of Garp                                                                                                                                                                     | 178        |

| A.2   | Structure of the reconfigurable array.                                                                                                                                                         | 179        |

| A.3   | Internal wiring within the array (independent of the memory buses)                                                                                                                             | 179        |

| A.4   | Simplified logic block schematic.                                                                                                                                                              | 181        |

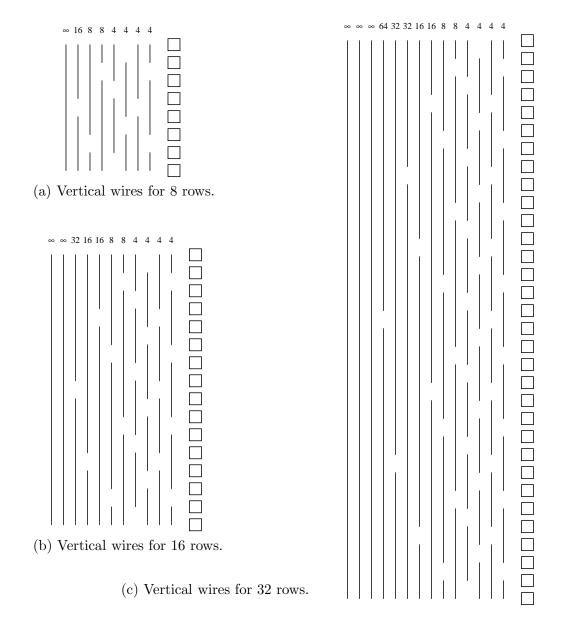

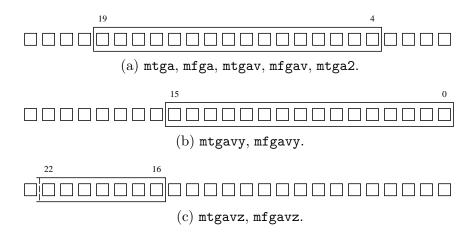

| A.5   | The vertical wires (V wires) for arrays of various sizes.                                                                                                                                      | 183        |

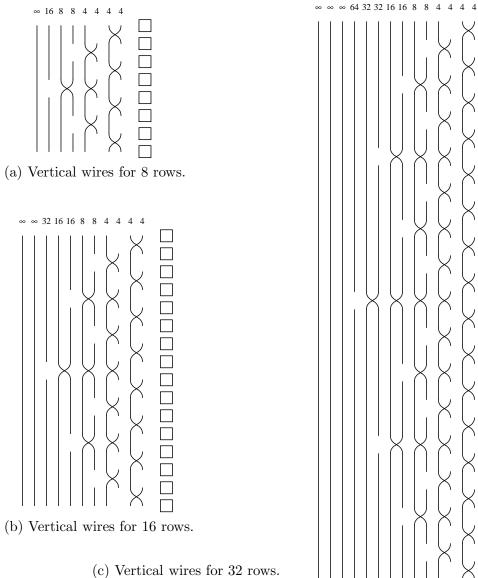

| A.6   | Twisting of the vertical wires to obtain a recursive structure.                                                                                                                                | 184        |

| A.7   | The horizontal wires between two rows.                                                                                                                                                         | 186        |

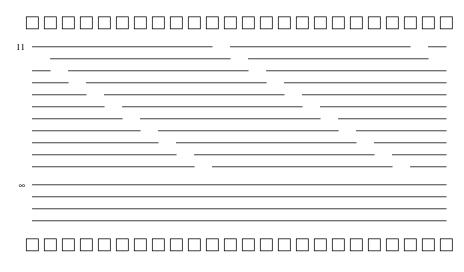

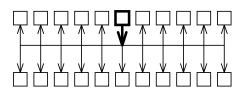

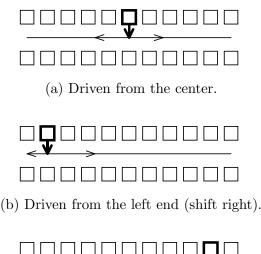

| A.8   | The logic blocks reachable via an H wire driven from the center.                                                                                                                               | 187        |

| A.9   | The three options for driving the H wires below a row.                                                                                                                                         | 187        |

|       | Logic block configuration encoding.                                                                                                                                                            | 188        |

|       | Configuration encoding for logic block inputs.                                                                                                                                                 | 188        |

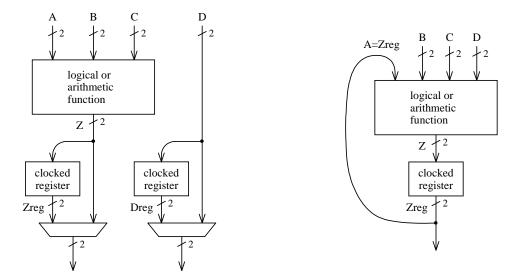

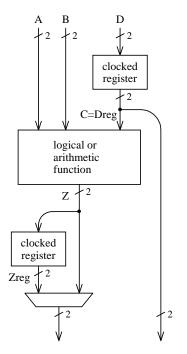

|       | Configuration encoding for logic block registers and outputs. $\dots$ $\dots$ $\dots$ Use of the $D$ input as a completely separate path for routing or copying.                               | 189<br>191 |

|       | Using an internal register as a logic block input.                                                                                                                                             | 191        |

|       | Delaying one logic block input using the $D$ path.                                                                                                                                             | 191        |

|       | Delaying the $Z$ output using the $D$ path                                                                                                                                                     | 192<br>192 |

|       | Reading values over the memory buses into internal registers configured as                                                                                                                     | 134        |

| 11.11 | logic block inputs.                                                                                                                                                                            | 192        |

| A 18  | A more complete logic block diagram.                                                                                                                                                           | 193        |

|       | The function mode encodings.                                                                                                                                                                   | 194        |

|       | Table mode (mode = $000$ ).                                                                                                                                                                    | 195        |

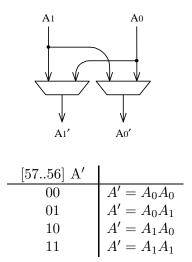

|       | The crossbar functions and encoding.                                                                                                                                                           | 195        |

|       | Interpretation of the lookup table in table mode.                                                                                                                                              | 195        |

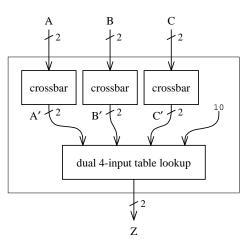

|       | Split table mode (mode = $001$ , mx = $01$ )                                                                                                                                                   | 196        |

|       | Interpretation of the lookup table in split table mode                                                                                                                                         | 196        |

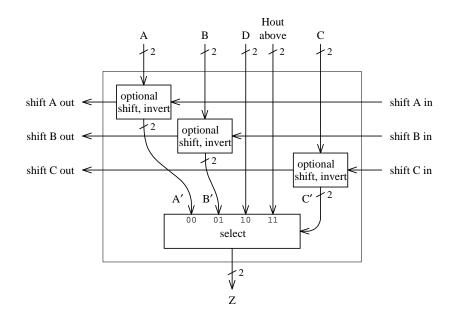

| A.25  | Select mode (mode = $011$ , mx = $00$ ).                                                                                                                                                       | 197        |

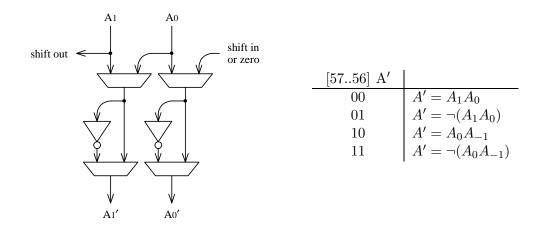

|       | The shift-invert functions and encoding.                                                                                                                                                       | 197        |

| A.27  | Partial select mode (mode = $011$ , mx = $01$ ).                                                                                                                                               | 199        |

| A.28  | Carry chain mode (mode = $101$ ).                                                                                                                                                              | 200        |

| A.29  | Interpretation of the lookup table in carry chain mode                                                                                                                                         | 200        |

| A.30  | Operation of the carry chain                                                                                                                                                                   | 201        |

| A.31  | The result functions for modes using the carry chain.                                                                                                                                          | 201        |

| A.32  | Triple add mode (mode = 111). $\ldots$                                                                                                                                                         | 202        |

| A.33  | Interpretation of the lookup table in triple add mode                                                                                                                                          | 202        |

| A.34  | The set of logic blocks read or written by various processor instructions.                                                                                                                     | 208        |

|       | Control block configuration encoding.                                                                                                                                                          | 222        |

| A.36  | Control block signals.                                                                                                                                                                         | 223        |

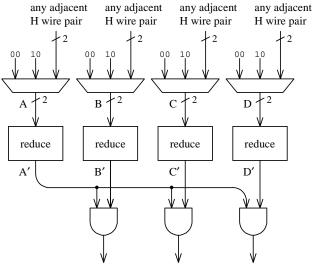

| A.37 | The reduction functions.                                                      | 223  |

|------|-------------------------------------------------------------------------------|------|

| A.38 | Valid connection to a control block.                                          | 223  |

| A.39 | Configuration encoding for a control block in processor interface mode        | 224  |

| A.40 | Configuration encoding for a control block in memory interface mode           | 225  |

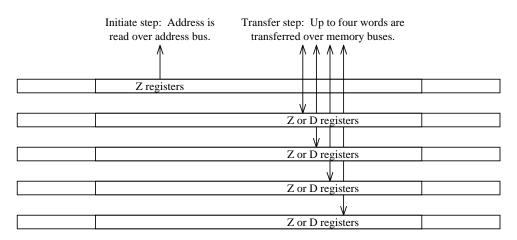

| A.41 | The two steps of a memory access initiated by the array.                      | 225  |

| A.42 | Memory interface configuration fields associated with the initiate step of a  |      |

|      | demand memory access.                                                         | 226  |

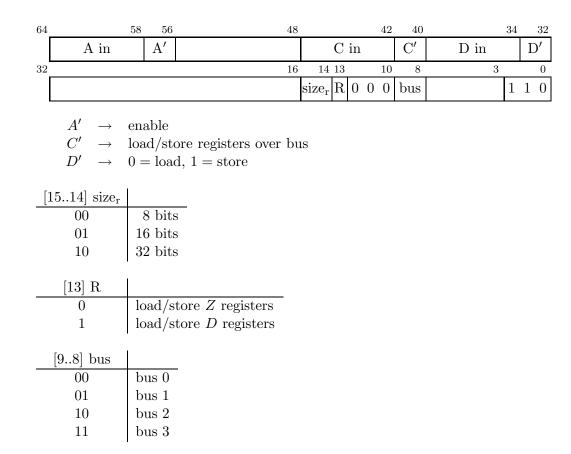

| A.43 | Memory interface configuration fields associated with the transfer step of a  |      |

|      | memory access.                                                                | 228  |

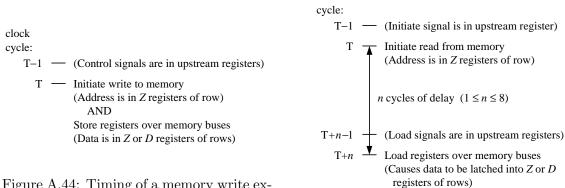

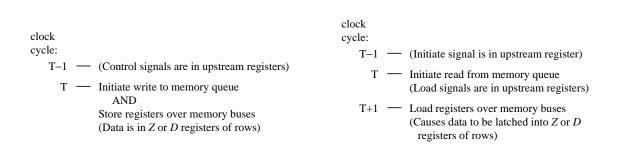

| A.44 | Timing of a memory write executed by the array.                               | 228  |

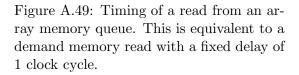

| A.45 | Timing of a memory read executed by the array                                 | 228  |

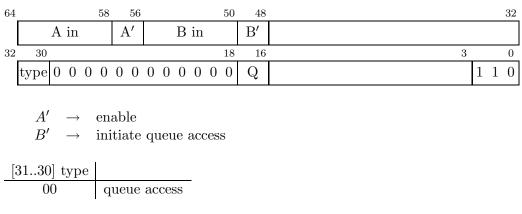

| A.46 | Format of a queue control record.                                             | 231  |

|      | Memory interface configuration fields associated with the initiate step of a  |      |

|      | memory queue access.                                                          | 232  |

| A.48 | Timing of a write to an array memory queue.                                   | 232  |

| A.49 | Timing of a read from an array memory queue.                                  | 232  |

| D 1  |                                                                               | 000  |

| B.1  | The fewest power-of-2 terms that sum to each odd integer up to 85.            | 239  |

| B.2  | Layout in the Garp array of a multiplier taking two unsigned 16-bit variables | 0.40 |

|      | and calculating a 32-bit product.                                             | 240  |

# List of Tables

| $2.1 \\ 2.2$                                                                                          | A sampling of FPGA chips available from Xilinx in 2000                                                                                                                                                                                                                                    | $\begin{array}{c} 13\\ 15\end{array}$                       |

|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 3.1<br>3.2                                                                                            | Approximate formulas for area, latency, and turnaround for the different arithmetic styles                                                                                                                                                                                                | $\begin{array}{c} 49\\ 50 \end{array}$                      |

| 3.3<br>3.4<br>3.5                                                                                     | Relative total area supposing each retiming register takes 2.5% as much area<br>as the rest of the logic block                                                                                                                                                                            | 50<br>54                                                    |

|                                                                                                       | ranging from 4 to 32.                                                                                                                                                                                                                                                                     | 56                                                          |

| $ \begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \end{array} $                                             | Examples of primitive operations implemented in Garp's reconfigurable array.<br>Array features employed by various operations Basic processor instructions for controlling the reconfigurable array Comparison of Garp with other research designs                                        | 72<br>72<br>74<br>78                                        |

|                                                                                                       |                                                                                                                                                                                                                                                                                           |                                                             |

| $5.1 \\ 5.2$                                                                                          | Synopsis of hand-coded benchmarks                                                                                                                                                                                                                                                         | 113                                                         |

|                                                                                                       | The number of calls to strlen or strcpy needed to cover the initial config-<br>uration loading time and achieve parity with the UltraSPARC A representative set of benchmark test cases, sorted approximately by speedup,                                                                 | 127                                                         |

| 5.2<br>5.3                                                                                            | The number of calls to <b>strlen</b> or <b>strcpy</b> needed to cover the initial config-<br>uration loading time and achieve parity with the UltraSPARC A representative set of benchmark test cases, sorted approximately by speedup,<br>with the factors limiting further improvements | 127<br>128                                                  |

| 5.2<br>5.3<br>5.4                                                                                     | The number of calls to strlen or strcpy needed to cover the initial config-<br>uration loading time and achieve parity with the UltraSPARC A representative set of benchmark test cases, sorted approximately by speedup,<br>with the factors limiting further improvements               | 127<br>128<br>129                                           |

| 5.2<br>5.3                                                                                            | The number of calls to <b>strlen</b> or <b>strcpy</b> needed to cover the initial config-<br>uration loading time and achieve parity with the UltraSPARC A representative set of benchmark test cases, sorted approximately by speedup,<br>with the factors limiting further improvements | 127<br>128                                                  |

| 5.2<br>5.3<br>5.4<br>5.5                                                                              | The number of calls to strlen or strcpy needed to cover the initial config-<br>uration loading time and achieve parity with the UltraSPARC A representative set of benchmark test cases, sorted approximately by speedup,<br>with the factors limiting further improvements               | 127<br>128<br>129<br>130                                    |

| <ul> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>5.8</li> </ul> | The number of calls to strlen or strcpy needed to cover the initial config-<br>uration loading time and achieve parity with the UltraSPARC A representative set of benchmark test cases, sorted approximately by speedup,<br>with the factors limiting further improvements               | 127<br>128<br>129<br>130<br>131<br>132<br>134               |

| $5.2 \\ 5.3 \\ 5.4 \\ 5.5 \\ 5.6 \\ 5.7 \\ 5.8 \\ 5.9 \\$                                             | The number of calls to strlen or strcpy needed to cover the initial config-<br>uration loading time and achieve parity with the UltraSPARC A representative set of benchmark test cases, sorted approximately by speedup,<br>with the factors limiting further improvements               | 127<br>128<br>129<br>130<br>131<br>132<br>134<br>135        |

| 5.2 $5.3$ $5.4$ $5.5$ $5.6$ $5.7$ $5.8$ $5.9$ $5.10$                                                  | The number of calls to strlen or strcpy needed to cover the initial config-<br>uration loading time and achieve parity with the UltraSPARC A representative set of benchmark test cases, sorted approximately by speedup,<br>with the factors limiting further improvements               | 127<br>128<br>129<br>130<br>131<br>132<br>134<br>135<br>137 |

| 5.2 $5.3$ $5.4$ $5.5$ $5.6$ $5.7$ $5.8$ $5.9$ $5.10$ $5.11$                                           | The number of calls to strlen or strcpy needed to cover the initial config-<br>uration loading time and achieve parity with the UltraSPARC A representative set of benchmark test cases, sorted approximately by speedup,<br>with the factors limiting further improvements               | 127<br>128<br>129<br>130<br>131<br>132<br>134<br>135        |

| 5.2 $5.3$ $5.4$ $5.5$ $5.6$ $5.7$ $5.8$ $5.9$ $5.10$ $5.11$                                           | The number of calls to strlen or strcpy needed to cover the initial config-<br>uration loading time and achieve parity with the UltraSPARC A representative set of benchmark test cases, sorted approximately by speedup,<br>with the factors limiting further improvements               | 127<br>128<br>129<br>130<br>131<br>132<br>134<br>135<br>137 |

| Distribution of wire hops for each logical connection between logic blocks. | 141                                                                       |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Inherent memory access patterns for the benchmark configurations, and the   |                                                                           |

| memory access resources actually used.                                      | 147                                                                       |

| Peak memory bandwidth requirements of each benchmark configuration.         | 147                                                                       |

|                                                                             |                                                                           |

|                                                                             |                                                                           |

| UltraSPARC and to Garp using Callahan's garpcc.                             | 158                                                                       |

| Added instructions.                                                         | 211                                                                       |

|                                                                             |                                                                           |

|                                                                             | 210                                                                       |

| Configuration of the carry chain for the comparison $a \neq b$              | 236                                                                       |

| Configuration of the carry chain for the comparison $a < b$                 | 236                                                                       |

| Configuration of the carry chain for the addition $a + b$                   | 237                                                                       |

|                                                                             | Inherent memory access patterns for the benchmark configurations, and the |

#### Acknowledgments

First, I would like to thank my advisor, John Wawrzynek, for his generous support and encouragement over the last several years. Without his unflagging confidence this project would never have been completed. Thanks also to the Berkeley Computer Science faculty for graciously extending me the time to bring this dissertation to fruition.

Thanks to my cohort on the Garp project, Tim Callahan, for his quiet friendship and for stoically listening to my various monologues and also my regular gripings about poor software. With his work on the Garp C compiler, Tim has helped make the project a success and increased its impact in the community.

Equal thanks to all my other officemates, notably Will Chang, Ngeci Bowman (the dancing Shmoo), William Tsu, Joe Gebis, and the two Greeks, Christoforos Kozyrakis and Stelios Perissakis, for many distracting discussions about religion, politics, language, culture, history, travel, photography, the stock market, intellectual property law, and some-times even computer architecture and software. Before he left to join the faculty at MIT, Krste Asanović helped sharpen my thinking about computer architecture and other subjects. Thanks also to Dave Johnson and the other folks at ICSI and the Cal Hiking and Outdoor Society (CHAOS), to the people I played ultimate with, and to my friend Dave Blackston, for helping me keep life in perspective. Thanks to Jim Beck for his always enjoyable commentary about everything.

Graduate assistants Kathryn Crabtree and Peggy Lau deserve applause for helping all us graduate students negotiate the rules and paperwork accompanying every phase of our progress towards that coveted degree.

My graduate work has been funded in part by DARPA's Adaptive Computing Systems program, grant DABT63-96-C-0048, by ONR grant N00014-92-J-1617, by NSF grant CDA 94-01156, as well as by donations from Xilinx and Hewlett-Packard.

Last but not least, I would like to recognize the continued support of my family over these many years.

# Chapter 1

# Introduction

Throughout its history in the last fifty years, digital electronics technology has improved exponentially over time, doubling in performance roughly every 18 months while device sizes and costs have shrunk correspondingly. In line with this growth, the number of transistors available for constructing a commodity microprocessor currently doubles every two years or so. With such persistent evolution in computer components, computer architecture must be constantly reexamined and reinvented. Designs that were excellent only a decade ago may be hopelessly simplistic today, while techniques that were once prohibitively expensive have today become the norm. Intuition based on the current state of the art may not be a good judge of what the future will bring.

In the last decade, out-of-order superscalar processors have developed as the standard for desktop microprocessors. It is widely believed, however, that we are fast reaching the limits of this paradigm. As superscalar issue width grows, its overhead increases quadratically, while at the same time, opportunities for exploiting more instruction-level parallelism seem to grow ever scarcer. As we approach the day when a single chip holds 100 million transistors—literally enough to pack 30 vintage Intel Pentiums onto one die—it seems doubtful that superscalar designs by themselves will make the most of the available potential.

One alternative being considered for the future is based on the technology of *field* programmable gate arrays (FPGAs). It should be obvious that every application would be best served by custom circuitry targeted specifically for it; and, in fact, application-specific integrated circuits (ASICs) are often made in response to special needs. But no one can afford to turn out a custom chip for every application he wants to run; and even when

they are feasible, state-of-the-art ASICs become more expensive every day. As technology has improved, a market has grown up instead for versatile off-the-shelf parts that can be programmed to emulate arbitrary digital circuits in place of ASICs. FPGAs are one class of such devices, distinguished by their ability to be reprogrammed (reconfigured) any number of times.

The versatility and reprogrammability of FPGAs comes at a price. Only a few years ago, the algorithms that could be implemented in a single FPGA chip were fairly small. In 1995, for example, the largest FPGAs could be programmed for circuits of about 15,000 logic gates at most. Since a fast 32-bit adder requires a couple hundred gates, the capabilities of such devices were somewhat bounded.

More recently, though, FPGAs have reached a size where it is possibile to implement reasonable subpleces of an application in a single FPGA part. This has led to a new concept for computing: if a processor were to include one or more FPGA-like devices, it could in theory support a specialized application-specific circuit for each program, or even for each stage of a program's execution. The unlimited reconfigurability of an FPGA permits a continuous sequence of custom circuits to be employed, each optimized for the task of the moment. Because FPGAs scale better than superscalar techniques, such designs have the potential to make better use of continuing advances in device electronics in the long term.

The idea of *reconfigurable computing* has been a subject of research for a decade, but most projects have investigated the potential of connecting one or more commercial FPGAs to an existing microprocessor via a standard external bus such as the PCI bus. If reconfigurable computing is really to become the computing paradigm of the future, the main parts must be brought closer together. Only a few studies have considered integrating a processor and FPGA into a single device, with the two tailored to cooperate closely with each other; and so there remain important questions about how such a device might be built and programmed, and how it would fit within an existing general-purpose computing framework. Such questions must be addressed before the bigger issue of whether reconfigurable computing is really a good model can be answered.

This thesis attempts to make progress on the question of whether reconfigurable computing will be a viable option for future general-purpose computers. The succeeding chapters contain the following:

- A look at the fundamentals of computing machines, followed by a summary of past work on reconfigurable computing and an articulation of the purpose of this research project.

- An exploration of numerous issues arising from the integration of reconfigurable hardware into a processor.

- The presentation of a plausible architecture for a reconfigurable-enhanced processor, and an examination of the feasibility of implementing it efficiently in VLSI.

- A summary of the development and simulation tools created for the proposed architecture, and then the quantitative results from a handful of benchmarks by which the design was evaluated.

- Lastly, a brief retrospective of weaknesses in the proposed architecture and lessons learned in the design.

The thesis closes with conclusions and some opinions about the direction of research in reconfigurable computing.

# Chapter 2

# **Background and Motivation**

This chapter first reviews the fundamentals of computation and considers why reconfigurable computing might be important in the future. It then lays out the focus of the research, and ends by summarizing related work.

## 2.1 The potential for reconfigurable computing

#### 2.1.1 Computing devices

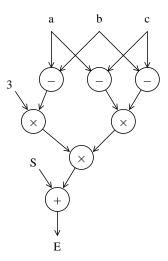

Any computation can be represented as a combination of abstract data-flow and control-flow graphs, with the nodes in the graphs being *primitive operations* such as integer addition or comparison. Figure 2.1 has an example of a data-flow graph for a short expression. The primary function of a computer is to evaluate such graphs mechanically so as to accomplish some goal. Of course, real computer processors do not operate on such abstract graphs directly; instead, programs are encoded as a collection of machine instructions which can be executed one after another in a specific sequence. But this is just an artifact of the design of the machine, intended originally to simplify the processor's task (and perhaps the programmer's, too). Modern processors, in fact, re-expose instruction level parallelism by dynamically decoding short sequences of machine instructions into their corresponding data- and control-flow forms before executing them. Regardless of how a program is physically encoded, data-flow and control-flow graphs represent the *true* computation being performed.

To evaluate the computational primitives in the graphs (addition, multiplication,

Figure 2.1: A data-flow graph for a simple expression.

etc.), processors include one or more *functional units*, each capable of performing a certain class of functions. A simple processor may have a single all-purpose functional unit known as an ALU (arithmetic and logic unit) that can only execute one operation at a time. More sophisticated processors (superscalar, VLIW) attempt to utilize multiple functional units of different kinds simultaneously to execute programs faster.

In concept, the functional units are all a computer needs to evaluate the operations in a data-flow graph. In practice, a computer must also support the physical movement of data among functional units, as well as to and from memory. Computers with multiple functional units clearly have to move data between them, and this not always as trivial as it might sound. But even for a simple processor with a single ALU, there is never more than a small amount of data that can be stored very close to the ALU at one time. A practical general-purpose computer must have a memory hierarchy, with the fastest and smallest memory (usually the registers) closest to the functional units, and increasingly slower but more capacious memory correspondingly farther away. Moving data between different levels of memory, either explicitly or implicitly, is thus another indispensible computer operation.

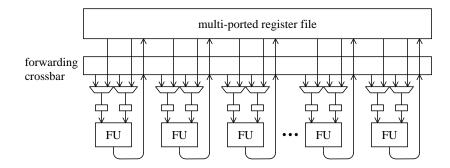

Figure 2.2 shows a simple diagram of a superscalar or VLIW processor with many functional units. For each clock cycle, an attempt is made to execute as many primitive operations as possible on the available functional units. A *forwarding crossbar* carries the output of all units back around to the functional unit inputs, so that the next set of operations can be executed in the next clock cycle with minimum delay. A multi-ported

Figure 2.2: The core of an aggressive superscalar or VLIW processor. The boxes labeled FU are the functional units. The small rectangles are registers preceding the functional units; there may be other such registers not shown.

Figure 2.3: An application-specific pipeline for computing the graph in Figure 2.1.

register file forms the highest level of the memory hierarchy and can be used to store values over multiple cycles. Although the ideal is to use every functional unit every clock cycle, no processor can achieve this for all programs because of the data and control dependencies inherent in practical algorithms. The flexibility of the functional units, forwarding crossbar, and register file is what makes a standard processor *programmable*, capable of executing an arbitrary application with decent performance, even applications not thought of when the processor was built.

The antithesis of a programmable processor is an ASIC (application-specific integrated circuit). In an ASIC, functional units can be dedicated to individual program operations and wired together to match precisely the calculation being performed. Figure 2.3 shows, for example, how an application-specific pipeline might be layed out to perform the calculation of the data-flow graph of Figure 2.1. The advantages an ASIC has over a programmable processor are threefold:

- Considerably less overhead is needed to control the mapping of functional units to operations and the routing of data values between them. On a programmable processor this overhead is manifest both in time and in die area.

- With smaller specialized functional units and less overhead circuitry around each one, more functional units can be fit into the same die area.

- Because the operation of each functional unit is known and planned out in advance, functional unit idleness can be minimized. On a programmable processor, certain kinds of functional units might never be used by a specific application.

Obviously, by their very definitions, a programmable device cannot be an ASIC and vice versa. However, as we shall see, *reconfigurable* devices such as FPGAs share characteristics of both processors and ASICs. On the one hand, FPGAs can implement ASIC-style circuits, while on the other, they are infinitely reprogrammable and thus immanently general-purpose. This leads to the question of whether reconfigurable hardware can capture some of the advantages of ASICs within a general-purpose computing environment.

#### 2.1.2 Utilizing growing hardware resources

In the past, FPGAs were too modest to compete with relatively efficient superscalar processors, but this relationship may be changing. Electronic devices continue to grow smaller and faster every day. The benefits of faster transistors and wires are obvious; that they are also smaller means we get more of them for the same cost. Market forces provide a strong incentive to find a way to use these added resources to improve each new processor generation.

Most of the real work of a processor is done in the functional units, so that is an obvious place to focus. Additional transistors can be employed in the functional units in at least three ways:

• Individual functional units can be made faster by reengineering them for speed at the expense of die area. For example, a one-bit-at-a-time iterative multiplier could be

replaced by a much larger and faster array multiplier. There are physical limits to this approach, however. If the processor already has array multipliers, opportunities for improving multiplication further will be less dramatic.

- New functional units can be added for functions that previously required a sequence of other operations. This is exactly what happened, for example, when floating-point functional units were originally added to processors, and the same is happening again today with small-SIMD operations (MMX, VIS, etc.). By expanding the different kinds of functional units, however, the likelihood is increased that some will be unused by an application.

- More copies of existing kinds of functional units can be added. This is the easiest route to contemplate, but the hardest to make actually productive. Aside from the increased hardware complexity of having more functional units to juggle, new degrees of parallelism must be found in the software, or the new units will sit perpetually idle.

Despite the difficulties, increased parallelism is the only viable path once opportunities for the first two options have petered out. Modern superscalar and VLIW processors are already committed to 6- to 8-way instruction issue, and more is being considered.

Software contains roughly three classes of parallelism that can be exploited:

- *Thread parallelism* is between independent threads of execution, each executing a separate sequence of instructions. One example would be when a subroutine contains two or more separate loops that have no dependencies between them, in which case the loops could all be executed simultaneously.

- Inter-iteration parallelism exists when the iterations of a single loop are all mutually independent of one another and thus can be executed in parallel. This is also known as *data parallelism* or *vector parallelism*, being the kind of parallelism that vector processors profit by. A classic matrix multiply or fast Fourier transform has inter-iteration parallelism that grows with the sizes of the operand arrays.

- Instruction-level parallelism (ILP) exists among operations within a single thread of control, such as within a single loop iteration. The short expression in the example of Figure 2.1, for instance, has 3-way ILP between the three subtractions, allowing the three operations to be executed at the same time.

#### 2.1.3 Limitations of superscalar and VLIW processors

In the 1990's, desktop processors adopted superscalar techniques to exploit ILP. By definition, a superscalar processor accepts a sequential instruction stream and discovers parallelism among the instructions dynamically and automatically. The basic model of Figure 2.2 is followed, with a forwarding crossbar and multi-ported register file. An extralarge register file and automatic register renaming are also commonly used to overcome false dependencies among the registers.

For all their popularity, superscalar machines are among the least efficient at exploiting parallelism. At 6-way issue, more effort is usually expended in testing instruction dependencies and controlling instruction issue than actually executing operations. This issue overhead grows quadratically with the number of functional units. Also under pressure to grow quadratically are the forwarding crossbar and register file (the register file because both its size in bits and number of ports must be increased). A 16-way superscalar processor would thus require tremendous overhead just to keep all its units busy.

VLIW (very long instruction word) processors eliminate much of the instruction issue overhead by relegating to the programmer or compiler the task of scheduling instruction execution to take maximum advantage of ILP. The work that a superscalar processor does on the fly to find ILP and avoid false dependencies (by register renaming) is done in advance before the program is run. Wide VLIW processors are also known to resist quadratic growth of the register file and crossbar, typically segmenting them such that the "crossbar" is not fully connected and not every register is accessible to every functional unit. These limitations make the VLIW processor more difficult to schedule for but also more efficient.

Nevertheless, the circuitry needed to issue new instructions to the functional units and reroute the crossbar every clock cycle remains a potential source of inefficiency even for VLIW processors. Furthermore, neither superscalar nor VLIW designs can take advantage of thread parallelism. Since the greatest sources of parallelism in programs are often interiteration and thread parallelism as opposed to simple ILP, this will eventually be exposed as a serious shortcoming.

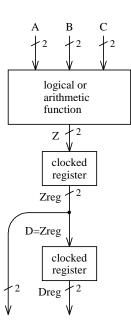

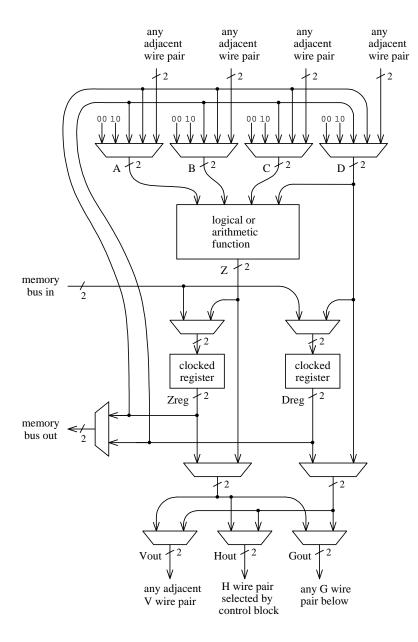

Figure 2.4: A model of a reconfigurable device analogous to Figure 2.2 for a traditional processor. An important aspect not visible in the figure is the fact that a reconfigurable device generally does not take a cycle-by-cycle instruction stream but instead is *reconfigured* between spurts of execution.

#### 2.1.4 Reconfigurable computing as a new model

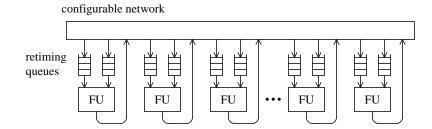

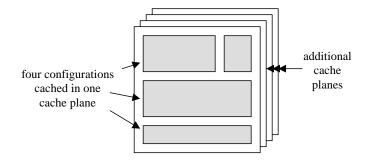

Reconfigurable computing is one alternative to the superscalar and VLIW paradigms. Figure 2.4 illustrates a reconfigurable device along the lines of the previous processor diagram. The main distinction between a reconfigurable device and a standard processor is in the instruction stream: in its purest form, a reconfigurable device has no cycle-by-cycle instruction stream. Rather, the device is *configured* by loading a complete specification of the function of each part of the device at once. Once configured, the intention is for the device to run in that configuration for a decent interval before being reconfigured. Each configuration mimics an ASIC-like circuit, like that of Figure 2.3, specialized for the particular task at hand. Changing configurations might take anywhere from a few clock cycles to a few thousand cycles. In accordance with the simpler programming mechanism, the dynamic forwarding crossbar is replaced by a less flexible *configurable network* for making static connections among the functional units; and short queues of *retiming registers* associated with each functional unit take the place of the traditional processor's shared, multi-ported register file.

The familiar 90-10 rule asserts that 90% of execution time is consumed by about 10% of a program's code, that 10% generally being inner loops. Reconfigurable devices excel in those cases where the computation represented by a configuration is repeated many times, so that the time required to load a configuration can be amortized over a long execution time and/or overlapped with other execution. When all of an application's important loop bodies can be configured to fit within the reconfigurable machine (one at a time), there would seem to be no need for the overhead of a fully dynamic instruction fetch and issue

Figure 2.5: A more practical hybrid machine, combining a traditional processor with a reconfigurable device.

mechanism, allowing the machine to be leaner and more efficient.

By reducing the hardware to just the essentials needed to support computation, the reconfigurable design scales better to larger sizes than the more complex superscalar and VLIW styles. Although a naive expansion of the configurable network would cause it to grow quadratically with the number of functional units, it actually only needs to grow enough to support the connectivity required by real applications. Furthermore, unlike a superscalar or VLIW machine, reconfigurable hardware can easily exploit not only simple ILP but also inter-iteration and thread parallelism, making reconfigurable computing wellpoised to work with very large numbers of functional units.

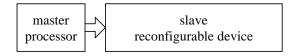

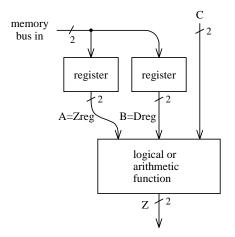

#### 2.1.5 The hybrid machine

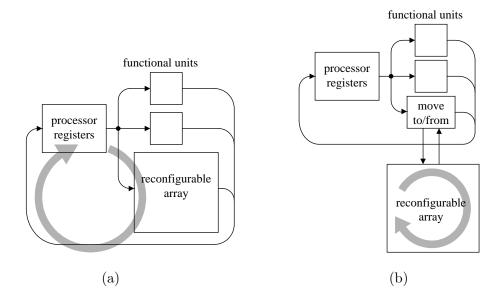

The corollary of the 90-10 rule is that 90% of a program's code accounts for only 10% of its execution time. In practice, reconfigurable devices get bogged down on the large parts of programs that are never executed with enough repetition to justify the time it takes to load a configuration for them. A practical compromise, therefore, is to couple a reconfigurable device with a traditional-style processor as in Figure 2.5, in order to exploit the strengths of each. With this organization, the reconfigurable hardware is used to execute the innermost loops (or *kernels*) of an application, while the modest traditional processor handles the mass of code between kernels.

In such a hybrid architecture, it makes sense to have the reconfigurable part be subservient to the traditional processor for at least two reasons: (1) the traditional processor executes the control code which logically ties together the various kernels the reconfigurable device will perform, and (2) execution on the traditional processor then becomes the default condition, allowing the new machine to fit in more easily with existing computing practice. The master processor can even be made instruction-set-compatible with an existing processor architecture to leverage existing development tools and operating systems.

Figure 2.6: The reconfigurable structure from Figure 2.4 as it appears in a commercial FPGA.

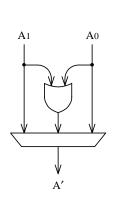

Figure 2.7: A canonical logic block function. Four single-bit inputs are taken from the configurable network and used to index into a 16-entry table of possible outputs. The box labeled R is a one-bit register in which the output can be optionally latched before being sent back over the configurable network to other logic blocks.

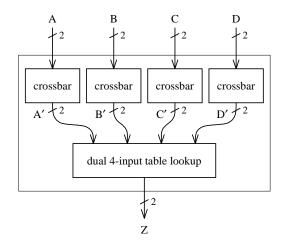

### 2.2 FPGAs

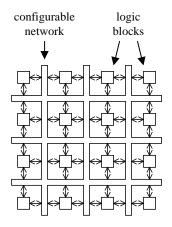

The most common reconfigurable devices today are FPGAs; these are independently packaged parts marketed both as prototyping platforms and as reconfigurable alternatives to ASICs. In a commercial FPGA, the basic structure from Figure 2.4 is reshaped into two dimensions to look more like Figure 2.6, with the functional units of the earlier diagram broken into a larger number of *logic blocks* that are individually rather small. The canonical logic block is often considered to be a lookup table that takes four bits of input and generates one bit of output, as shown in Figure 2.7. By filling in the table with the right bits, any four-input logic function can be realized. Various studies have suggested that four inputs is a good size for these lookup tables, trading off utility (how powerful the blocks are) against utilization (what fraction of their power ends up idle) [65, 66].

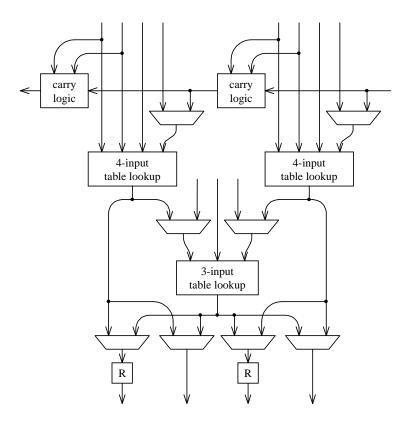

Logic blocks in actual FPGAs tend to be more complex than a single lookup table; Figure 2.8 has a similar diagram for a Xilinx 4000-series logic block, which has two fourinput lookup tables and an extra three-input table, for a total of eleven bits of input and four bits of output [71, 81]. Dedicated carry chain circuitry at the top of the figure makes it easy to gang together a line of logic blocks to form a relatively fast multi-bit adder. This diagram in fact ignores many additional details, such as the way Xilinx's two 16-bit lookup tables can be used together as 32 bits of random access memory, or the options available

Figure 2.8: Simplified view of a Xilinx 4000-series logic block. The block has eleven input bits and four output bits, plus special carry chain hardware for basic arithmetic operations.

|                  |           | number of 4-input | bytes of on-chip |

|------------------|-----------|-------------------|------------------|

|                  |           | lookup tables     | data RAM         |

| 3.3 V            | XC4036XLA | $6,\!156$         | 0                |

|                  | XC4052XLA | $9,\!196$         | 0                |

|                  | XC4085XLA | $14,\!896$        | 0                |

| $2.5 \mathrm{V}$ | XC40150XV | $24,\!624$        | 0                |

|                  | XC40250XV | 40,204            | 0                |

| $2.5 \mathrm{V}$ | XCV300    | 6,144             | 8,192            |

|                  | XCV600    | $13,\!824$        | 12,288           |

|                  | XCV1000   | $24,\!576$        | $16,\!384$       |

| 1.8 V            | XCV812E   | 18,816            | 143,360          |

|                  | XCV1000E  | $24,\!576$        | 49,152           |

|                  | XCV2000E  | 38,400            | 81,920           |

|                  | XCV3200E  | $64,\!896$        | 106,496          |

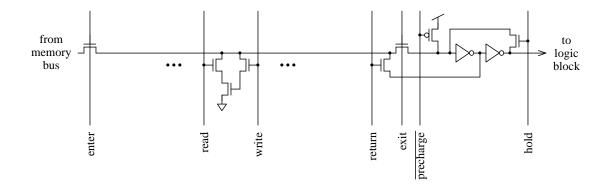

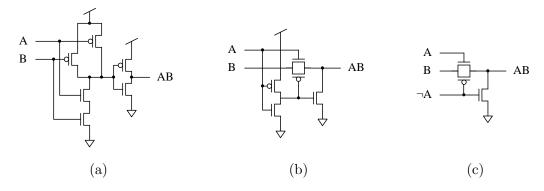

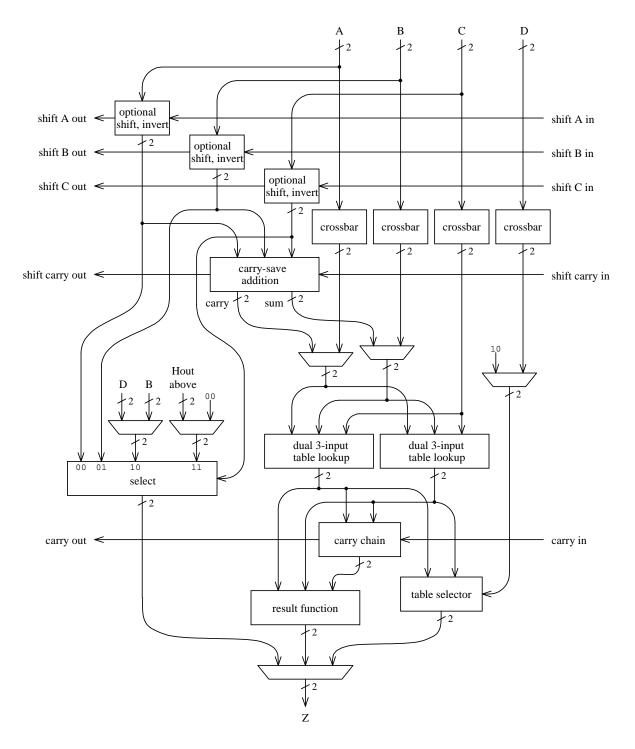

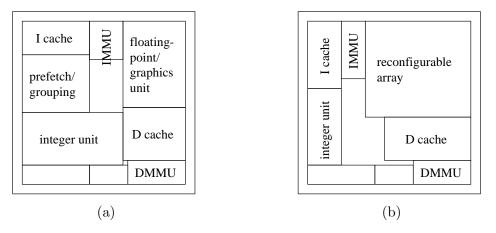

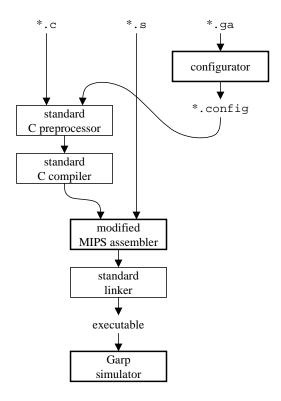

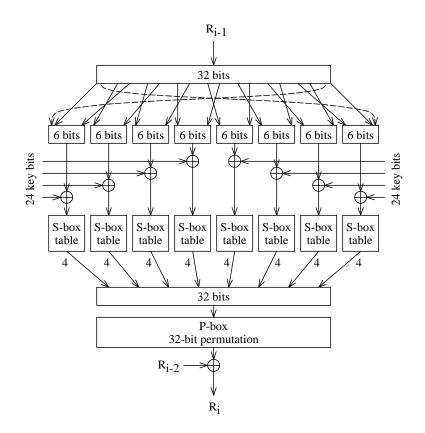

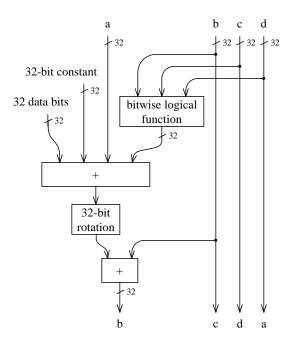

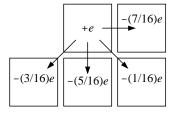

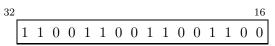

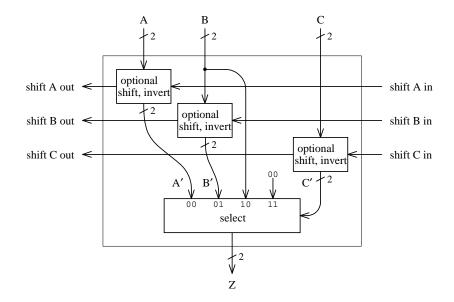

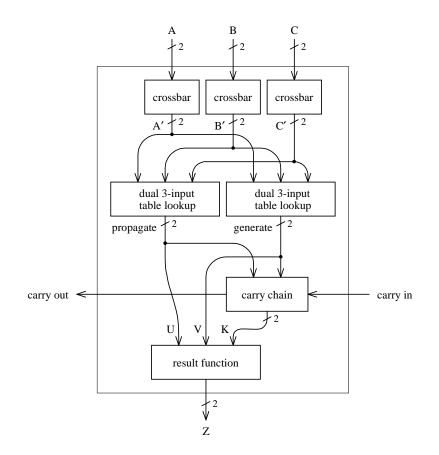

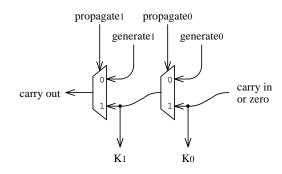

Table 2.1: A sampling of FPGA chips available from Xilinx in 2000. All the devices have additional capabilities beyond just the lookup tables and data memory listed.